| Load Current (mA) |

DVDD: 1000

AVDD: 300 |

| Channel |

4 |

| Power Supply (Min) (V) |

VIN1: 0.6

VIN2: 3 |

| Power Supply (Max) (V) |

VIN1: 2

VIN2: 5.5 |

| Vout (V) |

DVDD: 0.6V~1.8V

AVDD: 1.2V~4.3V |

| Vdropout (mV) |

DVDD: 100@0.8A

AVDD: 98@0.3A |

| Iq (Typ) (μA) |

65 |

| PSRR @1KHz(dB) |

DVDD: 71@10mA

AVDD: 89@50mA |

| Output Noise (μVrms) |

DVDD: 90@30mA

AVDD: 10@30mA |

| Discharge |

Programmable |

| Output options |

Programmable |

| Temperature |

-40℃~85℃ |

| IO Level (V) |

1.8 |

| Package (mm) |

DFN 2X2-10L |

VIN1 input voltage range: 0.6V to 2V

DVDD1/2 output voltage range: 0.6V~1.8V

DVDD1/2 dropout voltage: 100mV@0.8A

DVDD1/2 output drive capability: 1A Min.

The max of DVDD1/2 output drive capability can be set to 1.3A by config I2C

VIN2 quiescent current: typical: 65uA

VIN2 shutdown current: typical: 0.25uA

VIN2 input voltage range: 3V to 5.5V

VIN2 UVLO voltage value: 2V

AVDD1/2 output voltage range: 1.2V~4.3V

AVDD1/2 output typical 98mV dropout voltage at 300mA load, VOUT=2.8V

AVDD1/2 output drive capability: 300mA Min.

The max of AVDD1/2 output drive capability can be set to 600mA by config I2C

AVDD1/2 power supply rejection ratio: typical 92dB (IOUT=30mA, freq=1KHz)

AVDD1/2 noise: typical 10uVrms (IOUT=30mA, BW=10Hz to 100KHz)

DFN 2mmX2mmX0.75mm-10L package

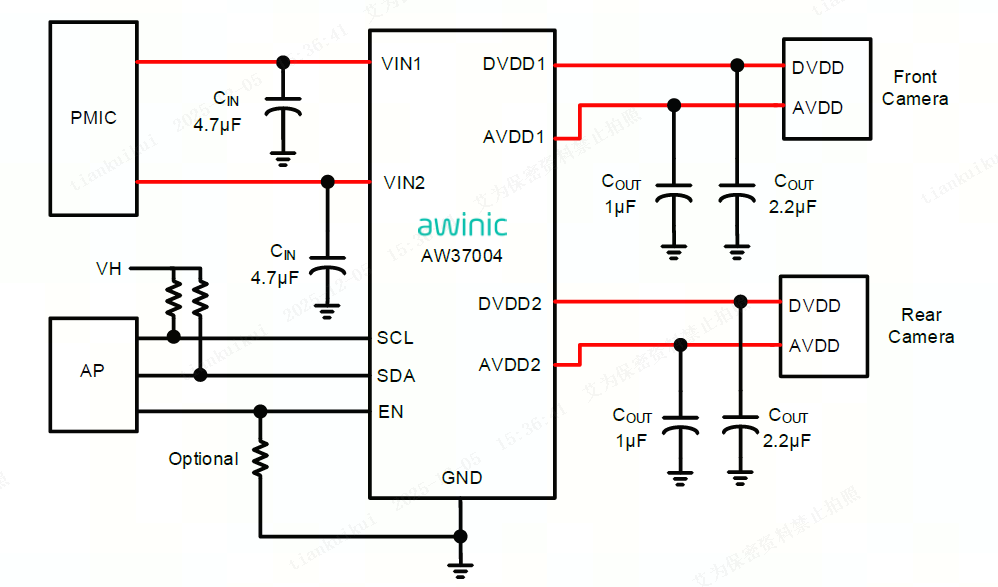

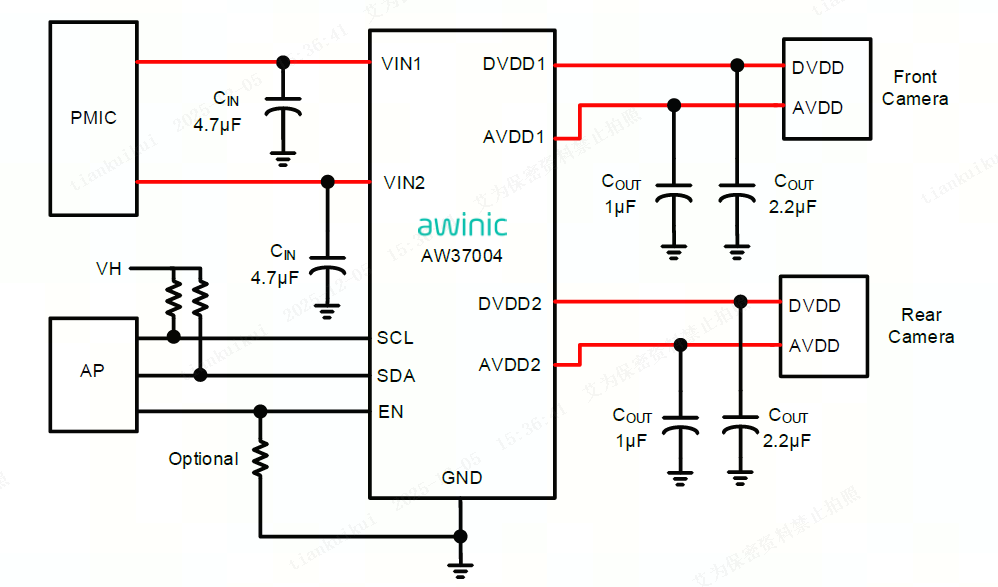

AW37004DNR is a 4-ch integrated LDO PMIC for camera applications include 2-ch DVDD, 2-ch AVDD, with 400KHz high speed I2C interface, the function setting is flexible such as power sequence, output discharge. The chip enable control support EN pin control and I2C control.

Due to high load current and lower working voltage of DVDD, AW37004DNR used N-MOSFET LDO architecture without charge pump for 2-ch DVDD LDO. DVDD LDO input source is VIN1 and VIN2 is the bias voltage. Ultra low dropout voltage of DVDD LDOs is designed for high efficiency and lower power dissipation purpose. For the AVDD, AW37004DNR used P-MOSFET LDO architecture. The input source is VIN2. Due to high performance requirement of AVDD, AW37004DNR’s AVDD used special circuit design and optimized pin assignment which is easy for system PCB layout.